刚开始弄AD9516,看了几天文档,还是没理解透,就到网上找资料,进一步的了解,结果在这个帖子上和好友们慢慢讨论,也搞明白了http://forum.eepw.com.cn/thread/228366/1,在这里非常感谢好友lianggui5的热心解答,下面就和大家一起分享下我学到的一些关键点。

一.芯片的工作模式

AD9516可设置3种工作模式,包括外部的VCO,CLK以及内部的VCO,这根据芯片的外围连接就可以看出来;

二.内部的PLL工作原理

如果芯片工作在外部CLK模式下,参考输入(REFIN/REFIN_n)先经R分频模块,再通过R延时模块(延时可调节)后进入PFD(相位/频率检测)模块一端,同时VCO产生的信号通过N分频模块(预分频P.P+1和A/B计数模块)和N延时模块(延时可调)后进入PFD的另一端;PFD用于比较两信号的频率和相位差,产生与之成比例的信号传输给CP(电荷泵),电荷泵通过外接环形滤波器连接至VCO的控制端。电荷泵根据PFD的信号对环形滤波器的连接点充(放)电以达到VCO电压调节目的,使VCO输出和参考输入与PFD的频率和相位完全匹配,此时锁存相位,输出同步;

三.最初令人头痛的分频寄存器配置

除了PLL用于产生稳定的VCO所涉及到的寄存器R,A,B外,分频寄存器还包括时钟输出分频寄存器(VCO Divider),输出时钟通道分频寄存器(Output Divider)。时钟输出分频器可以随意设置为2--6中的任意整数,输出时钟通道分频寄存器可选用1--32中的任意整数作为分频参数。需要注意的是,PLL的R,A,B这3个寄存器的配置相互制约,必须合理配置,片内的VCO才能工作在由参考输入提供的频率范围内,否则将导致不能锁存锁相模块。这些制约包括:PFD输入频率范围,A和B计数器输入最高频率,R、A和B值大小。设计时,考虑到这些制约以及设计的需要,就能正确配置内部分频寄存器

片内VCO的计算

F_vco=(F_ref/R)x(PxB+A);

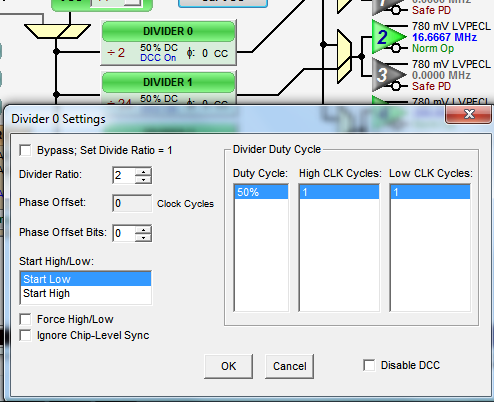

还有输出通道分频寄存器配置,在AD9516评估软件上点击DIVIDER 0,改变divider Ratio就可以改变分频系数,这里的系数是由右边的High CLK cycles和low clk cycles求和得出,可通过输出通道相应的寄存器配置改变;

四.对于从评估软件导出来的文件,里面的数据可大致参考,因为我在调试的时候,就出现对于评估软件输出的频率,跟我实际用示波器测的结果不一样;还有对于配置数据的发送,这个没有什么先后顺序;数据的发送方式与SPI协议相兼容,若果没有输出频率,首先确定你配置的数据写进去了没有,这个可以通过对芯片进行读操作,我当时就因为没写进去,一开始老以为是配置数据的问题,原来是我的spi协议没写好;以上是我的一些理解,如有什么不好的地方,可以讨论;

评估软件下载:

AD9516_17_18EvalSetup1.1.0.rar

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。